TSMC 이번 주에 자사의 차세대 트랜지스터 기술을 설명했습니다. IEEE 국제 전자 장치 회의(IEDM) 샌프란시스코에서. N2 또는 2나노미터기술은 반도체 파운드리 거대 기업이 새로운 트랜지스터 아키텍처에 처음으로 진출한 것입니다. 나노시트 또는 게이트 올라운드.

삼성은 유사한 장치를 제조하는 프로세스를 갖고 있으며, 두 가지 모두 인텔 TSMC는 2025년에 생산할 것으로 예상하고 있습니다.

현재 TSMC의 가장 진보된 공정인 N3(3나노미터)에 비해 이 신기술은 최대 15% 속도 향상 또는 최대 30% 향상된 에너지 효율성을 제공하는 동시에 밀도를 15% 증가시킵니다.

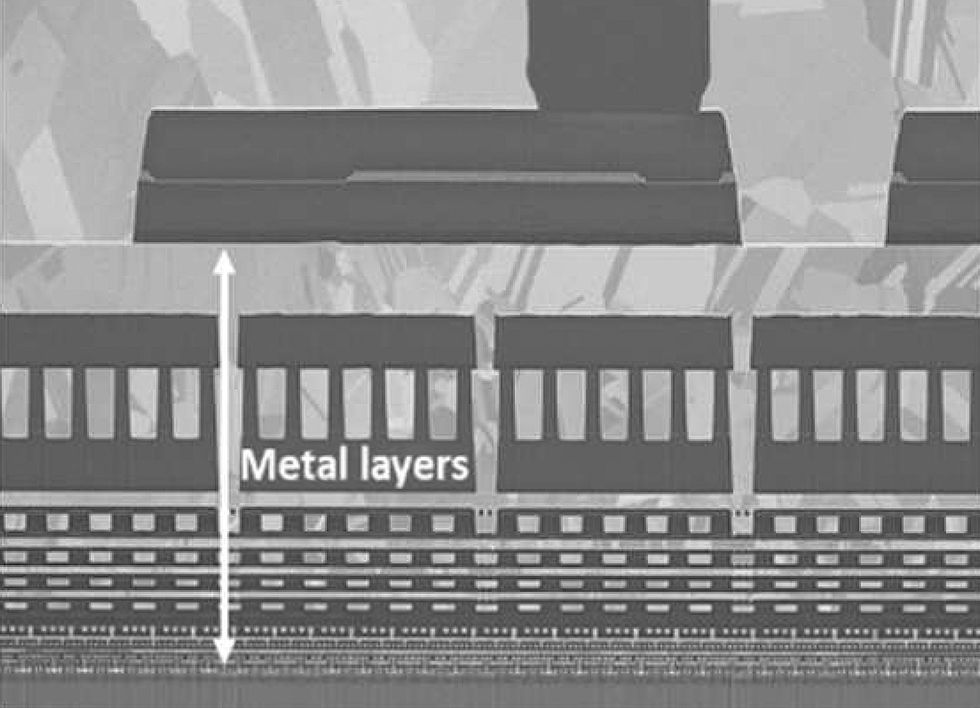

N2는 “4년 넘게 노력한 결실”이다. 제프리 예프TSMC의 R&D 및 첨단 기술 부사장은 IEDM의 엔지니어들에게 말했습니다. 오늘날의 트랜지스터는 FinFET중앙에 수직 실리콘 핀이 있습니다. 나노시트 또는 게이트 만능 트랜지스터는 대신 실리콘의 좁은 리본 스택을 갖습니다.

이러한 차이점은 장치를 통한 전류 흐름을 더 잘 제어할 수 있을 뿐만 아니라 엔지니어가 더 넓거나 더 좁은 나노시트를 만들어 더 다양한 장치를 생산할 수 있게 해줍니다. FinFET는 핀이 1개, 2개 또는 3개 있는 장치와 같이 장치의 핀 수를 곱함으로써만 이러한 다양성을 제공할 수 있습니다. 그러나 나노시트는 설계자에게 1.5개의 핀에 해당하거나 특정 논리 회로에 더 적합한 것과 같은 그라데이션 옵션을 제공합니다.

Nanoflex라고 불리는 TSMC의 기술은 다양한 나노시트로 제작된 다양한 로직 셀을 가능하게 합니다. 동일한 칩의 너비. 좁은 장치로 만들어진 논리 셀은 칩의 일반 논리를 구성할 수 있고, 더 많은 전류를 구동하고 더 빠르게 전환할 수 있는 더 넓은 나노시트를 가진 논리 셀은 CPU 코어를 구성할 수 있습니다.

나노시트의 유연성은 프로세서의 주요 온칩 메모리인 SRAM에 특히 큰 영향을 미칩니다. 여러 세대에 걸쳐 6개의 트랜지스터로 구성된 이 핵심 회로는 다른 로직만큼 빠르게 줄어들지 않았습니다. 그러나 N2는 이러한 확장 정체의 연속을 깨뜨린 것으로 보이며, Yeap이 지금까지 가장 밀도가 높은 SRAM 셀이라고 설명한 결과는 평방 밀리미터당 38메가비트, 즉 이전 기술인 N3에 비해 11% 향상된 결과입니다. N3는 이전 제품에 비해 6%만 향상되었습니다. “SRAM은 게이트 올라운드(gate-all-around)로의 본질적인 이득을 얻습니다.”라고 Yeap은 말합니다.

미래의 게이트 만능 트랜지스터

TSMC가 내년 트랜지스터에 대한 세부 정보를 제공하는 동안 Intel은 업계가 이를 얼마나 오랫동안 축소할 수 있는지 살펴보았습니다. 인텔의 답변: 원래 생각했던 것보다 더 깁니다.

“나노시트 아키텍처는 실제로 트랜지스터 아키텍처의 마지막 개척지입니다.” 아시시 아그라왈Intel 부품 연구 그룹의 실리콘 기술자인 는 엔지니어들에게 말했습니다. 미래에도 상보형 FET(CFET) 2030년대 중반에 출시될 가능성이 있는 장치는 나노시트로 구성됩니다. 따라서 연구자들이 한계를 이해하는 것이 중요하다고 Agrawal은 말했습니다.

“우리는 벽에 부딪치지 않았습니다. 그것은 가능하며 여기에 증거가 있습니다. 우리는 정말 좋은 트랜지스터를 만들고 있습니다.” —인텔 산제이 나타라잔(Sanjay Natarajan)

인텔은 트랜지스터의 소스와 드레인 사이의 게이트가 차지하는 거리인 게이트 길이라는 중요한 배율 요소를 조사했습니다. 게이트는 장치를 통한 전류 흐름을 제어합니다. 게이트 길이를 줄이는 것은 역사적인 이유로 접촉 폴리 피치(CPP)라고 불리는 표준 논리 회로 내에서 장치 간 최소 거리를 줄이는 데 중요합니다.

Agrawal은 “CPP 스케일링은 주로 게이트 길이에 따라 이루어지지만 10나노미터 게이트 길이에서는 정체될 것으로 예상됩니다.”라고 말했습니다. 10나노미터는 게이트 길이가 너무 짧아서 무엇보다도 장치가 꺼져 있어야 할 때 장치 전체에 너무 많은 전류가 누출될 수 있다고 생각했습니다.

Agrawal은 “그래서 우리는 10나노미터 이하로 밀어내는 것을 고려했습니다. Intel은 장치가 켜져 있을 때 전류가 흐르는 단일 나노시트만 장치에 갖도록 일반적인 게이트 전체 구조를 수정했습니다.

나노시트를 얇게 만들고 주변 물질을 수정함으로써 팀은 게이트 길이가 6nm에 불과하고 나노시트 두께가 3nm에 불과한 적절한 성능의 장치를 생산할 수 있었습니다.

결국 연구자들은 실리콘 게이트 만능 장치가 확장 한계에 도달할 것으로 예상하므로 Intel과 다른 곳의 연구자들은 나노시트의 실리콘을 다음과 같은 물질로 대체하기 위해 노력해 왔습니다. 2차원 반도체 이황화 몰리브덴과 같은. 하지만 6나노미터 결과는 한동안 2D 반도체가 필요하지 않을 수도 있음을 의미합니다.

“우리는 벽에 부딪힌 적이 없습니다.”라고 말합니다. 산제이 나타라잔Intel Foundry의 기술 연구 부문 수석 부사장 겸 총괄 관리자입니다. “그것은 가능합니다. 여기에 증거가 있습니다. 우리는 6나노미터 채널 길이에서 정말 좋은 트랜지스터를 만들고 있습니다.”