인텔, 삼성 및 TSMC와 같은 다람쥐의 거인은 실리콘 트랜지스터의 주요 부분이 두께가 몇 개 밖에되지 않는 반도체로 대체되는 미래를 참조하십시오. 그들은 그 목표를 향한 진전을보고했지만, 그 미래는 일반적으로 10 년 이상. 지금 MIT에서 시작된 스타트 업은 상업용 규모를 만들기위한 코드를 깨뜨렸다 고 생각합니다. 2D 반도체,,, 그리고 Chipmakers는 그 당시 절반에 고급 칩에 통합 할 것으로 기대합니다.

CDimension은 몰리브덴 이황화 성장 과정을 개발했습니다 (MOS22D 반도체, 저온 온도에서 실리콘에서 실리콘 회로의 기초가 손상되지 않을 것입니다. 기존 실리콘 회로 위의 2D 트랜지스터 층을 통합 할 수 있습니다. 멀티 계층 3D 칩 2D 장치에서.

CDimension CEO이자 공동 창립자는“많은 사람들이 2D 반도체를 여전히 실험실에있는 것으로 생각합니다. Jiadi Zhu. “그러나 CDimension은 2D 재료 성장을 위해 설계된 독점 도구를 가지고 있습니다. [2D materials] 문제 웨이퍼 규모의 균일 성, 장치 성능 및 변화, 장치 신뢰성 및 실리콘 제조 공정과의 호환성과 관련하여.” 종합하면, 2D 반도체는 산업 단계 개발 단계에 들어갈 준비가되어 있다고 그는 말했다.

Cdimension의 많은 계획의 대부분은 단일 층의 MOS를 키우는 데 사용하는 독점 과정에 달려 있습니다.2 전체 300 밀리미터 웨이퍼에 걸쳐 약 200 ℃에서 실리콘 및 기타 기판에서. 2D 재료는 화학 증기 증착에 의해 형성되며, 여기서 기화 된 전구체 화학 물질은 표면에 반응하여 코팅한다. 그러나 일반적으로 2D 재료를 만드는 반응은 1000 ° C 이상의 온도를 필요로합니다. 그것은 너무 높아 트랜지스터를 만드는 데 필요한 기본 구조를 손상시킬 것입니다. 오늘날 연구자들은 2D 반도체를 개별적으로 입금 한 다음 실리콘 웨이퍼로 섬세하게 전송하여 그 문제를 해결합니다. 그러나 Cdimension의 시스템은 손상없이 실리콘 웨이퍼의 재료를 바로 성장시킬 수 있습니다.

2D 반도체 사업

현재 스타트 업의 비즈니스의 일부는 2D 재료로 실리콘 웨이퍼를 배송하여 고객이이를 평가하고 장치를 구축 할 수있는 것입니다. 또는 고객은 이미 처리 된 웨이퍼를 보낼 수있어 실리콘 회로 나 구조물이 있도록 할 수 있습니다. 그런 다음 CDIMENSION은 MOS를 성장시킬 수 있습니다2 또는 그 위에 다른 2D 재료가 고객에게 다시 보냅니다. 따라서 2D 장치 레이어를 실리콘 회로와 통합 할 수 있습니다.

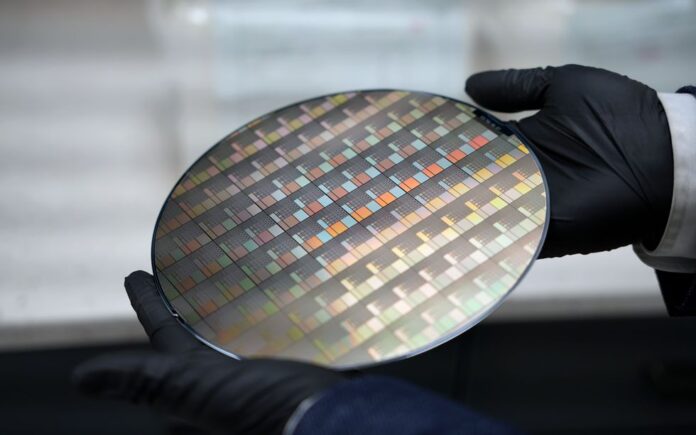

CDimension의 프로세스로 만든 테스트 웨이퍼는 현미경 아래에 있습니다.cdimension

CDimension의 프로세스로 만든 테스트 웨이퍼는 현미경 아래에 있습니다.cdimension

후자는 2D 반도체의 첫 번째 산업 진입 일 수 있습니다. Zhu는“우리는 실리콘과 2D 재료로 가능성을 보여줍니다. “그러나 2D 자료는 고도로 스케일 된 논리 장치에도 사용될 수 있습니다. 다음 단계가 될 수 있습니다.”

다람쥐는 좋아합니다 인텔,,, 삼성그리고 TSMC 미래의 트랜지스터에서 실리콘 나노 시트를 MOS로 대체하는 것을 목표로보고 된 연구2 및 다른 2D 반도체 IEEE 국제 전자 장치 회의 2024 년 12 월. 같은 회의에서 Zhu와 IEEE Fellow의 MIT 실험실의 동료들은 Tomás Palacios 그리고 징 콩 그 사실을 보여주었습니다 저온 합성은 MOS를 생성 할 수 있습니다2 트랜지스터 나노 시트 트랜지스터와 비슷한 여러 스택 채널이 있습니다. (Palacios는 CDIMension의 전략 고문입니다.) 장치를 축소함으로써, 팀은 이러한 장치가 전력 소비, 성능 및 이들이 점유하는 영역 측면에서 미래 10A (1 나노 미터) 노드의 요구 사항을 충족하고 초과 할 수 있다고 예측했습니다.

2D 반도체와 함께 가려는 큰 동기는 전력 소비를 줄이는 것입니다. 트랜지스터가 켜져있을 때 (동력)와 꺼져있을 때 (정전기) 전원이 손실됩니다. 2D 트랜지스터는 0.6 나노 미터가 넘기 때문에 오늘날의 실리콘 장치의 전압의 약 절반을 사용하여 작동 할 수있는 품질을 가지고있어 동적 전력을 절약 할 수 있습니다. 그들이 꺼져있을 때, 그것은 당신이 가장 걱정 해야하는 유출 전류입니다. 그러나 MOS2 실리콘의 값의 두 배 이상인 밴드 갭이있어 장치 전체에서 누출되기 위해서는 훨씬 더 많은 에너지가 필요하다는 것을 의미합니다. Zhu는 CDIMENSION의 재료를 사용하여 제조 된 장치는 실리콘 장치의 에너지의 1 분의 1만으로 소비되었다고 말합니다.

MOS 외에2전자 전도 (N- 타입) 반도체 인, 시작은 또한 P- 타입 반도체 인 텅스텐 디 셀레 나이드뿐만 아니라 육각형 붕소와 같은 2D 절연 필름을 제공한다. 2D 반도체가 향후 CMOS 칩에서 인수되면 전체 조합이 필요합니다.